# 1. Overview of X7083/X7043/X7023

#### 1-1 Introduction

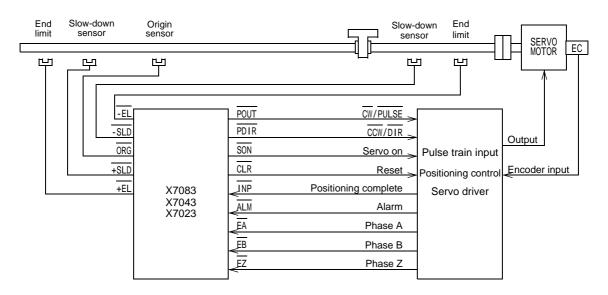

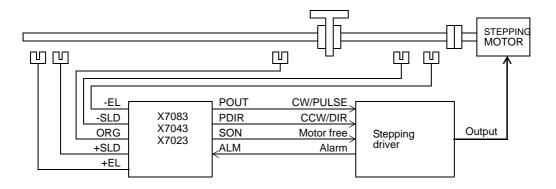

X7083/X7043/X7023 is an LSI that generates a pulse for controlling the speed and positioning of pulse train input-type servo motors and stepping motors. X7083 enables 8-axis control, X7043 enables 4-axis control, X7023 enables 2-axis control.

This unit is comprised of an S-shaped or linear acceleration/deceleration pulse generator, a linear interpolation divider, an automatic deceleration point calculator based on trapezoidal or triangular drive, multi-counter and encoder inputs that can be used as the current position counter or deviation counter, a return-to-origin sensor interface, a limit sensor interface, a servo drive interface, an 8-bit general-purpose input, and an 8-bit generalpurpose output.

Since X7083/X7043/X7023 provides an interface with a host CPU, it can be used as a peripheral LSI.

#### 1-2 Features

CPU interface

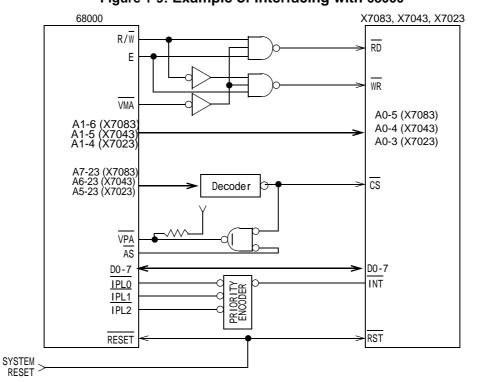

Applicable microcomputers: 80 series, 68 series, etc.

Address occupancy: 6 bits (64 bytes) for X7083, 5 bits (32 bytes) for X7043, and

4 bits (16 bytes) for X7023

Data bit width: 8 bits

Drive commands

Index drive:

Continuous pulse drive: Return-to-origin drive: Sensor positioning drive:

Drive modes

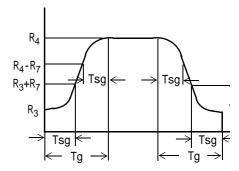

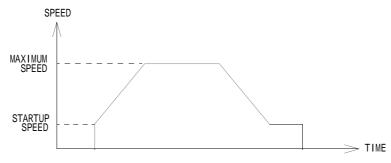

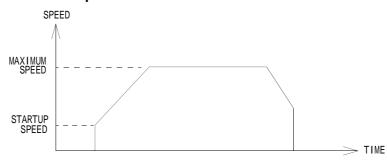

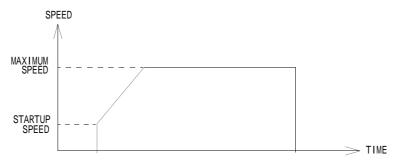

Acceleration/deceleration mode: S-shaped (sine, parabolic), linear

Deceleration start point: Automatic calculation, manual setting, offset setting

Synchronization mode: Multi-axis linear interpolation, sync start

Encoder counter

Number of counters: 2

Bit length: 24 bits/32 bits switchable

Count inputs: Internal pulse only, external-input pulses only, Internal pulse

and external-input pulses

Encoder converter inputs

Number of channels: 1 channel

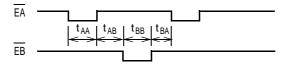

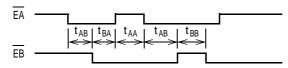

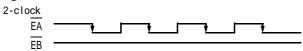

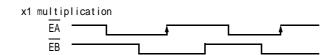

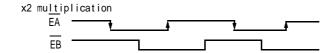

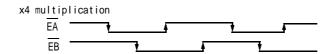

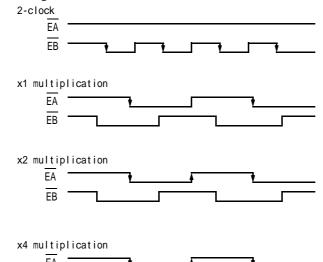

Input format: 2-clock, 2-phase clock with 90° phase error

1/2/4 multiplication Multiplication:

Comparator

Bit length:

Comparison targets: Register and counter, counter and counter

= , > Comparison methods:

Comparison output: 1 point ( = or > ), only for X7043 and X7023

I/O

#### X7083, X7043 and X7023

Inputs: 8

Outputs 8

Other functions

Independent setting functions for accelerator and decelerator

Timer function

Input filtering function

Interrupt function

I/O logic switching function

Status functions

Clock: 20.0 MHz (max.), 16.384 MHz or 19.6608 MHz recommended

Technology: CMOS

Power source: Internal voltage: 3.3 V IO voltage: 5 V or 3.3 V

Operating temperatures: 0 to +70

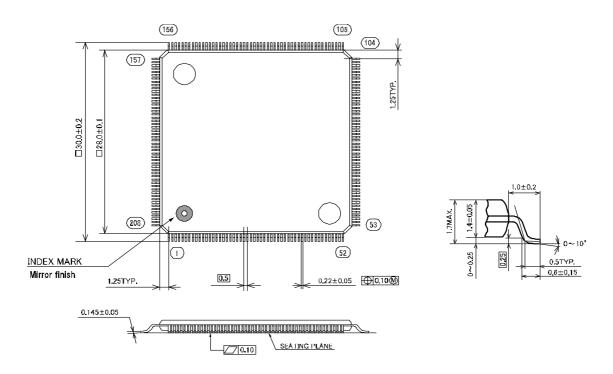

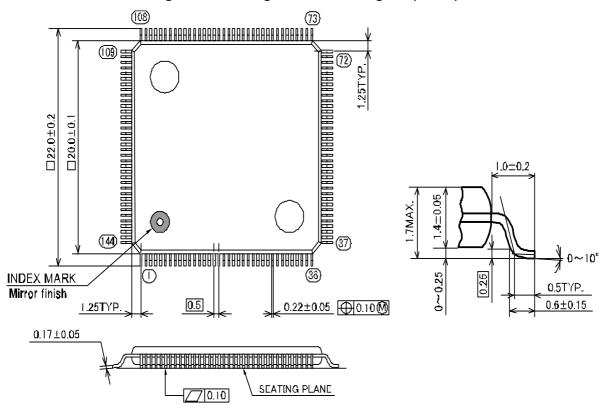

Package: X7083 208-pin LQFP 28 x 28 (mm)

X7043 144-pin LQFP 20 x 20 (mm) X7023 100-pin TQFP 14 x14 (mm) Lead-free specification: Sn-1 to 4Bi solder

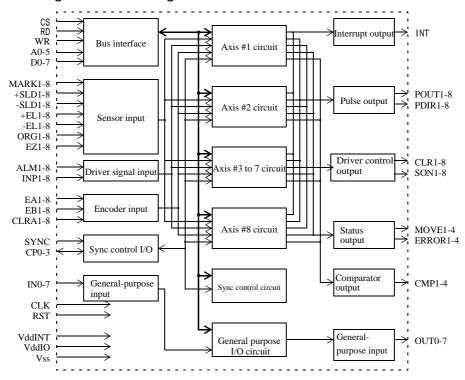

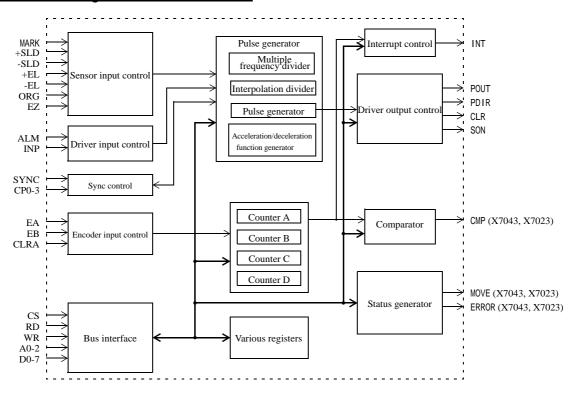

# 1-3 Block Diagram

Figure 1-1: Block Diagram

Overall Block Diagram and I/O Signals

#### Circuit Block Diagram for Axes #1 to #8

Only X7043 and X7023 have CP0-3, ERROR, and CMP. X7083 has axes #1 to #8, X7043 axes #1 to #4, and X7023 axes #1 to #2.

# 1-4 Specifications List

Table 1-1: Specifications List

| Item                                                           | Specifications                                                            |  |  |  |  |  |

|----------------------------------------------------------------|---------------------------------------------------------------------------|--|--|--|--|--|

| Supply voltage                                                 | Internal voltage 3.3 V ±10% I/O voltage 5 V ±10% or 3.3V ±5%              |  |  |  |  |  |

| Input/output level                                             | CMOS level                                                                |  |  |  |  |  |

| Max. input clock (f)                                           | 20.0 MHz (max), 16.384 MHz or 19.6608 MHz recommended                     |  |  |  |  |  |

| Max. output frequency                                          | Linear acceleration/deceleration: 5 Mpps                                  |  |  |  |  |  |

| Max. output frequency                                          | S-shaped acceleration/deceleration: 3.05 Mpps                             |  |  |  |  |  |

|                                                                | Approx. 8 ms to 131 s                                                     |  |  |  |  |  |

| Acceleration/deceleration time                                 | (16382  steps, f = 16.384  MHz)                                           |  |  |  |  |  |

| Output pulse count setting range (R <sub>1</sub> )             | 1 to 16,777,215                                                           |  |  |  |  |  |

| Deceleration start point setting range                         | 0 to 16,777,215 (manual setting)                                          |  |  |  |  |  |

| $(R_2)$                                                        | -8388608 to 8388607 (auto-calculated offset setting)                      |  |  |  |  |  |

| Frequency multiplication ratio setting                         | 1. 4005                                                                   |  |  |  |  |  |

| range (R <sub>0</sub> )                                        | 1 to 4095                                                                 |  |  |  |  |  |

|                                                                | Linear acceleration/deceleration, S-shaped acceleration/deceleration and  |  |  |  |  |  |

| Frequency setting step count (R <sub>3</sub> ,R <sub>4</sub> ) | deceleration point manual setting mode: 1 to 16383                        |  |  |  |  |  |

| Frequency setting step count $(K_3, K_4)$                      | S-shaped acceleration/deceleration and deceleration start point automatic |  |  |  |  |  |

|                                                                | calculation mode: 1 to 10000                                              |  |  |  |  |  |

| Acceleration/deceleration rate setting                         | 1 to 16383                                                                |  |  |  |  |  |

| range (R <sub>5</sub> ,R <sub>6</sub> )                        |                                                                           |  |  |  |  |  |

| S-shaped section setting range (R <sub>7</sub> )               | 1 to 8191                                                                 |  |  |  |  |  |

| Sensor input sensitivity setting range                         | 0 to 255                                                                  |  |  |  |  |  |

| (F)                                                            | Approx. 0.98 to 250 µs (f = 16.384 MHz)                                   |  |  |  |  |  |

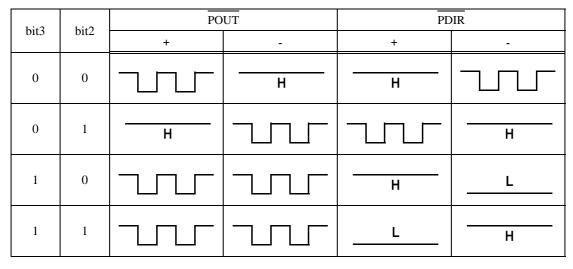

|                                                                | Outputs: Clock output: Gate control/2-clock switchable, logic switchable  |  |  |  |  |  |

|                                                                | 1-shot output: Approx. 1.9 µ s (f = 16.384 MHz), logic switchable         |  |  |  |  |  |

| Driver interface                                               | Servo ON output: General-purpose output                                   |  |  |  |  |  |

|                                                                | Inputs: Driver alarm input: 1 point per axis, logic switchable            |  |  |  |  |  |

|                                                                | Positioning end input: 1 point per axis, logic switchable                 |  |  |  |  |  |

|                                                                | End limit inputs: 2 points, +/- directions, logic switchable              |  |  |  |  |  |

|                                                                | Slow-down inputs: 2 points, +/- directions, logic switchable              |  |  |  |  |  |

| Sensor inputs                                                  | Slow-down/slow-down stop switchable                                       |  |  |  |  |  |

| _                                                              | Origin input: 2 points per axis, origin and Z phase, logic switchable     |  |  |  |  |  |

|                                                                | Mark sensor input: 1 point per axis, logic switchable                     |  |  |  |  |  |

|                                                                | Inputs: 8 points                                                          |  |  |  |  |  |

| General-purpose inputs/outputs                                 | Outputs: 8 points                                                         |  |  |  |  |  |

| Encoder interface                                              | Input: One channel per axis, 2 clocks, 1/2/4 multiplication               |  |  |  |  |  |

|                                                                | Sync start input: 1 point                                                 |  |  |  |  |  |

| Other inputs/outputs                                           | Counter clear inputs: 1 point per axis                                    |  |  |  |  |  |

| On and in a total                                              | Comparator output: 1 point per axis (only for X7043 and X7023)            |  |  |  |  |  |

| Operating temperatures                                         | 0 to +70°C                                                                |  |  |  |  |  |

| Storage temperatures                                           | -65 to +150°C                                                             |  |  |  |  |  |

|                                                                | X7083 208PIN LQFP 28 x 28 (mm)                                            |  |  |  |  |  |

| Dimensions                                                     | X7043 144PIN LQFP 20 x 20 (mm)<br>X7023 100PIN TQFP 14 x 14 (mm)          |  |  |  |  |  |

|                                                                | Lead-free specification Sn-1 to 4Bi solder                                |  |  |  |  |  |

|                                                                | Lead free specification on the solder                                     |  |  |  |  |  |

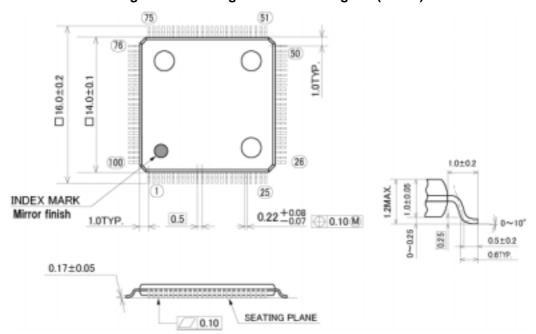

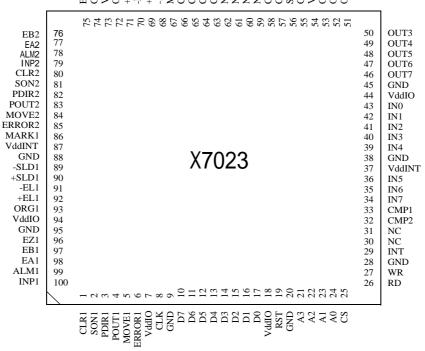

# 1-5 Package Dimension Diagram

Figure 1-2: Package Dimension Diagram (X7083)

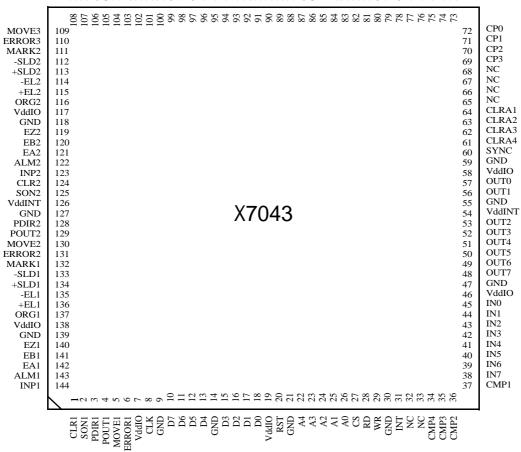

Figure 1-3: Package Dimension Diagram (X7043)

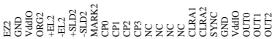

Figure 1-4: Package Dimension Diagram (X7023)

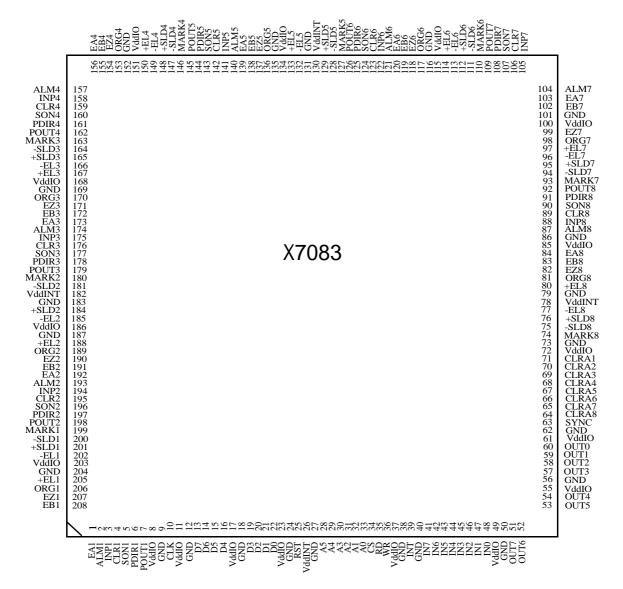

# 1-6 Pin Layout, Terminal Description

# 1-6-1 Terminal Description

**Table 1-2: Terminal Description**

| Terminal No.   X7043   X7023   Signal   I/O   Logic   Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |              |            | Table    |      | 1     | •                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------|------------|----------|------|-------|----------------------------------------------------------|

| 26, 78, 130, 182                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7       | Terminal No. |            | Signal   | I/O  | Logic | Description                                              |

| 130, 182                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | X7083   | X7043        | X7023      | Digital  | 1, 0 | Logic | Beschpuon                                                |

| 130, 182   8, 11, 17, 23, 37, 49, 55, 61, 72, 85, 100, 115, 134, 151, 168, 186, 203   9, 12, 18, 24, 27, 38, 40, 50, 183, 187, 204   10   8   8   CLK   I   + Duty 50 ±10%   This LSI can be accessed when this pin goes Low.   1   - Chip select signal. This LSI can be accessed when this pin goes Low.   33   26   24   A0   32   25   23   A1   31   24   22   A2   30   23   21   A3   32   25   23   A1   31   24   22   A2   30   23   21   A3   32   25   23   A1   32   28   26   This LSI can be accessed by from Low to High while CS is Low.   45 V ±10% or 3.3V ±5% power input.   +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.     +5 V ±10% or 3.3V ±5% power input.   | 26, 78, | 54 126       | 37 87      | VddINT   | _    |       | +3 3 V +10% power input                                  |

| 37, 49, 55, 61.       7, 19, 46, 58, 79, 98, 117, 138       7, 18, 44, 54, 73, 94       7, 18, 44, 54, 73, 94       7, 18, 44, 54, 73, 94       7, 18, 44, 54, 73, 94       7, 18, 44, 54, 73, 94       9, 14, 21, 90, 20, 28, 38, 45, 59, 80, 99, 118, 127, 139       9, 14, 21, 90, 40, 40, 40, 40, 40, 40, 40, 40, 40, 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -       | 0 ., 120     | 57, 67     |          |      |       | Total Power Imput                                        |

| 7, 19, 46, 58, 79, 98, 117, 138  117, 138  117, 138  117, 138  117, 138  117, 138  117, 138  117, 138  117, 138  117, 138  117, 138  117, 138  117, 138  117, 138  117, 138  117, 138  118, 127, 138, 44, 54, 73, 94  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  118, 127, 139  11 |         |              |            |          |      |       |                                                          |

| 72, 85, 100, 115, 134, 117, 138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         | 7, 19, 46,   |            |          |      |       |                                                          |

| 115, 134,   151, 168,   186, 203   18, 24   27, 38, 40, 50, 56, 62, 73, 79, 86, 101, 116,   131, 135,   152, 169,   183, 187, 204     25   20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |              |            | VddIO    | _    |       | +5 V ±10% or 3.3V ±5% power input.                       |

| 151, 168, 186, 203   9, 12, 18, 24, 27, 38, 40, 50, 56, 62, 73, 79, 86, 101, 116, 131, 135, 152, 169, 183, 187, 204   10   8   8   CLK   I   + Reference clock input. Max. input frequency 20 MHz. Duty 50 ±10%   Rest signal. The LSI is reset when Low input of more than 3 reference clock periods is input. Chip select signal. This LSI can be accessed when this pin goes Low.   35   28   26   RD   I   - Read enable signal. Data can be read out when CS is Low and RD is Low.   Write enable signal. Data can be loaded at the positive-going edge of WR from Low to High while CS is Low.   36   29   27   A4   22   A2   21   A3   31   24   22   A2   21   A3   29   22   - A4   28   A5   22   18   17   D0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |              | 54, 73, 94 |          |      |       |                                                          |

| 9, 12, 18, 24, 27, 38, 40, 50, 56, 62, 73, 79, 86, 101, 116, 131, 135, 152, 169, 183, 187, 204                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |              |            |          |      |       |                                                          |

| 27, 38, 40, 50, 56, 62, 73, 79, 86, 101, 116, 131, 135, 152, 169, 183, 187, 204       9, 20, 28, 38, 45, 55, 74, 88, 95       GND       -       age of the property of the                                                                     | -       |              |            |          |      |       |                                                          |

| 56, 62, 73, 79, 86, 101, 116, 130, 47, 55, 59, 80, 99, 118, 127, 139                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |              |            |          |      |       |                                                          |

| 86, 101, 116, 131, 135, 132, 169, 183, 187, 204       38, 45, 55, 74, 88, 95       38, 45, 55, 74, 88, 95       0 V power input.         10       8       8       CLK       I       + Reference clock input. Max. input frequency 20 MHz. Duty 50 ±10%         25       20       19       RST       I       - Rest signal. The LSI is reset when Low input of more than 3 reference clock periods is input.         34       27       25       T       - Chip select signal. This LSI can be accessed when this pin goes Low.         35       28       26       RD       I       - Read enable signal. Data can be read out when CS is Low and RD is Low.         36       29       27       WR       I       - Write enable signal. Data can be loaded at the positive-going edge of WR from Low to High while CS is Low.         33       26       24       A0         32       25       23       A1         31       24       22       A2         30       23       21       A3         29       22       -       A4         28       -       -       A5         22       18       17       D0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         | 9, 14, 21,   | 0 20 28    |          |      |       |                                                          |

| 131, 135,   159, 80, 99,   118, 127,   139                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         | 30, 47, 55,  |            |          |      |       |                                                          |

| 118, 127,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         | 59, 80, 99,  |            | GND      | -    |       | 0 V power input.                                         |

| 183, 187, 204                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         | 118, 127,    |            |          |      |       |                                                          |

| 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         | 139          | 86, 93     |          |      |       |                                                          |

| 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |              |            |          |      |       |                                                          |

| 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 204     |              |            |          |      |       | Reference clock input. Max. input frequency 20 MHz.      |

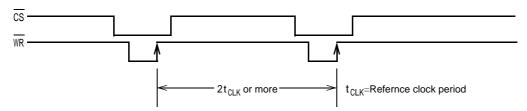

| 25   20   19   RST   I   - Rest signal. The LSI is reset when Low input of more than 3 reference clock periods is input.    34   27   25   CS   I   - Chip select signal. This LSI can be accessed when this pin goes Low.    35   28   26   RD   I   - Read enable signal. Data can be read out when CS is Low and RD is Low.    36   29   27   WR   I   - Write enable signal. Data can be loaded at the positive-going edge of WR from Low to High while CS is Low.    33   26   24   A0     32   25   23   A1     31   24   22   A2   30   23   21   A3   I   + 6-bit address bus from A0 (LSB) to A5 (MSB).    29   22   - A4   - A5   22   18   17   D0   D0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10      | 8            | 8          | CLK      | I    | +     |                                                          |

| 25   20   19   RST   I   -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |              |            |          |      |       |                                                          |

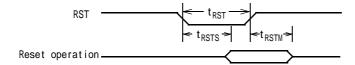

| 34   27   25   \overline{\overline{\color{\color{1}{1}}} - \overline{\color{\color{1}{1}}} - \overline{\color{1}{1}} \overline{\color{1}{1}} - \overline{\color{1}{1}} \overline{\color{1}{1}} \overline{\color{1}{1}} - \overline{\color{1}{1}} \overline{\color{1}} \overl   | 25      | 20           | 19         | RST      | I    | -     | -                                                        |

| Seed enable signal. Data can be read out when CS is Low and RD is Low.    36   29   27   WR   I   - Write enable signal. Data can be loaded at the positive-going edge of WR from Low to High while CS is Low.   33   26   24   A0     32   25   23   A1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.1     | 27           | 25         |          | _    |       |                                                          |

| 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 34      | 21           | 25         | CS       | ı    | -     | pin goes Low.                                            |

| Second    | 25      | 20           | 26         | <u> </u> | т    |       | Read enable signal. Data can be read out when CS is Low  |

| 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 33      | 20           | 20         | KD       | 1    | -     | and RD is Low.                                           |

| Soing edge of WR from Low to High while CS is Low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 36      | 29           | 27         | WR       | ī    | _     | Write enable signal. Data can be loaded at the positive- |

| 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |              |            |          |      |       | going edge of WR from Low to High while CS is Low.       |

| 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 33      | 26           | 24         | A0       |      |       |                                                          |

| 30 23 21 A3 I + 6-bit address bus from A0 (LSB) to A5 (MSB).  29 22 - A4  28 - A5  22 18 17 D0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 32      | 25           | 23         | A1       |      |       |                                                          |

| 30 23 21 A3 29 22 - A4 28 - A5 22 18 17 D0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31      | 24           | 22         | A2       | Ī    | +     | 6-bit address bus from A0 (LSR) to A5(MSR)               |

| 28 A5<br>22 18 17 D0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 30      | 23           | 21         | A3       | 1    | , '   | o on address ous from AU (LSD) to AJ (WSD).              |

| 22 18 17 D0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 29      | 22           | -          | A4       |      |       |                                                          |